Ngày 14/05/2024, Viện Công nghệ Thông tin, ĐHQGHN tổ chức seminar với chủ đề “Các kỹ thuật thiết kế mạch tích hợp tiên tiến”. Buổi seminar dưới sự chủ trì của GS.TS. Trần Xuân Tú – Viện trưởng, được tổ chức trực tiếp và trực tuyến trên nền tảng Zoom với sự tham gia của các nghiên cứu viên, nghiên cứu sinh của Viện Công nghệ Thông tin cùng với giảng viên, chuyên gia, sinh viên đến từ các trường đại học và doanh nghiệp.

Buổi seminar bắt đầu với báo cáo về “Ngăn chặn Satisfiability Attack bằng Decoy Key-Inputs”. Chuỗi cung ứng toàn cầu trong ngành công nghiệp bán dẫn đang gây ra nhiều lo ngại về an ninh như sản xuất IC quá mức, vi phạm sở hữu trí tuệ và giả mạo thiết kế. Khóa logic đã xuất hiện như một biện pháp để giải quyết những vấn đề này. Các đề xuất về khóa logic sẽ tạo ra các sai lệch đầu ra cao trong mạch nếu nó không được mở khóa bằng khóa đúng. Đây là điều kiện tiên quyết để làm cho mạch sản xuất không thể sử dụng được mà không có sự can thiệp của nhà thiết kế. Các cuộc tấn công SAT (Satisfiability Attack) là kiểu tấn công nhằm tái tạo lại khóa từ các dữ liệu được đoán trước và thiết kế khóa tương ứng. Diễn giả đã đề xuất một hệ thống khóa logic gọi là SKG-Lock nhằm ngăn chặn các cuộc tấn công SAT trong khi vẫn duy trì mức độ sai lệch đầu ra đáng kể bằng cách sử dụng khóa đầu vào mồi nhử (Decoy Key-Inputs).

Diễn giả Nguyễn Quang Linh hiện đang là Tiến sĩ tại hãng ST Microelectronics (Cộng hòa Pháp), đây là một hãng công nghệ toàn cầu chuyên tạo ra các công nghệ bán dẫn với tiêu chí thông minh hơn, thân thiện với môi trường hơn và bền vững hơn.

Báo cáo tập trung trình bày vào các nội dung:

- Cung cấp thông tin nền tảng về khóa logic, mức độ sai lệch đầu ra, tấn công SAT và các biện pháp đối phó hiện tại.

- Giới thiệu về SKG-Lock, phân tích mức độ an ninh chống lại tấn công SAT

- Các kết quả đánh giá về an ninh, mức độ sai lệch của đầu ra và chi phí thực thi của SKG-Lock

Bài trình bày trên đã đề xuất một phương pháp chống lại tấn công SAT dựa trên các cổng khóa có thể chuyển đổi và các đầu vào khóa mồi nhử. SKG-Lock cung cấp mức độ sai lệch đầu ra cao, cấu trúc tốt, khả năng chống chịu cao hơn so với các phương pháp hiện tại và chi phí thấp. Kiến trúc này cũng giúp chống lại các tấn công phân tích cấu trúc và tín hiệu.

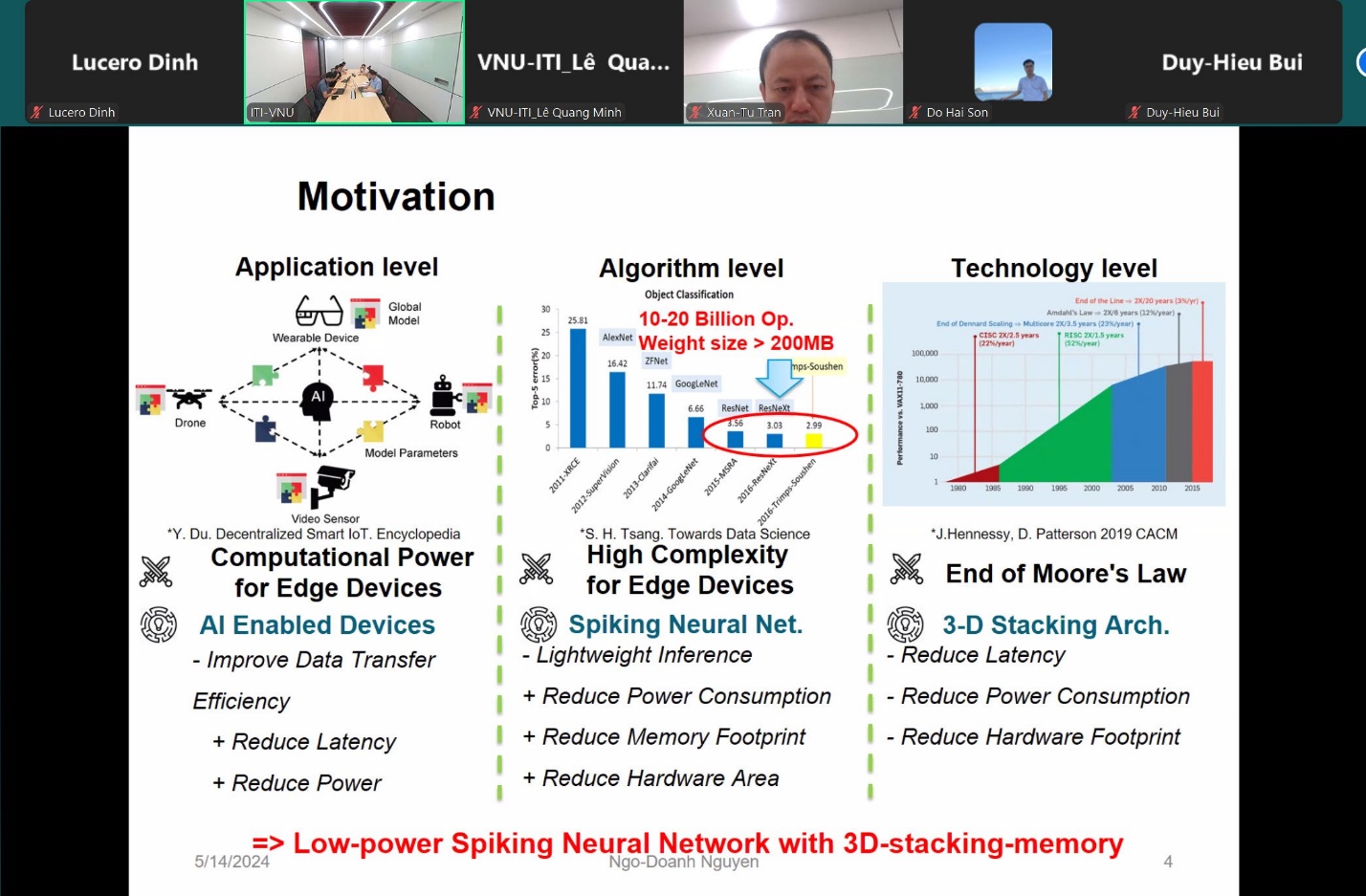

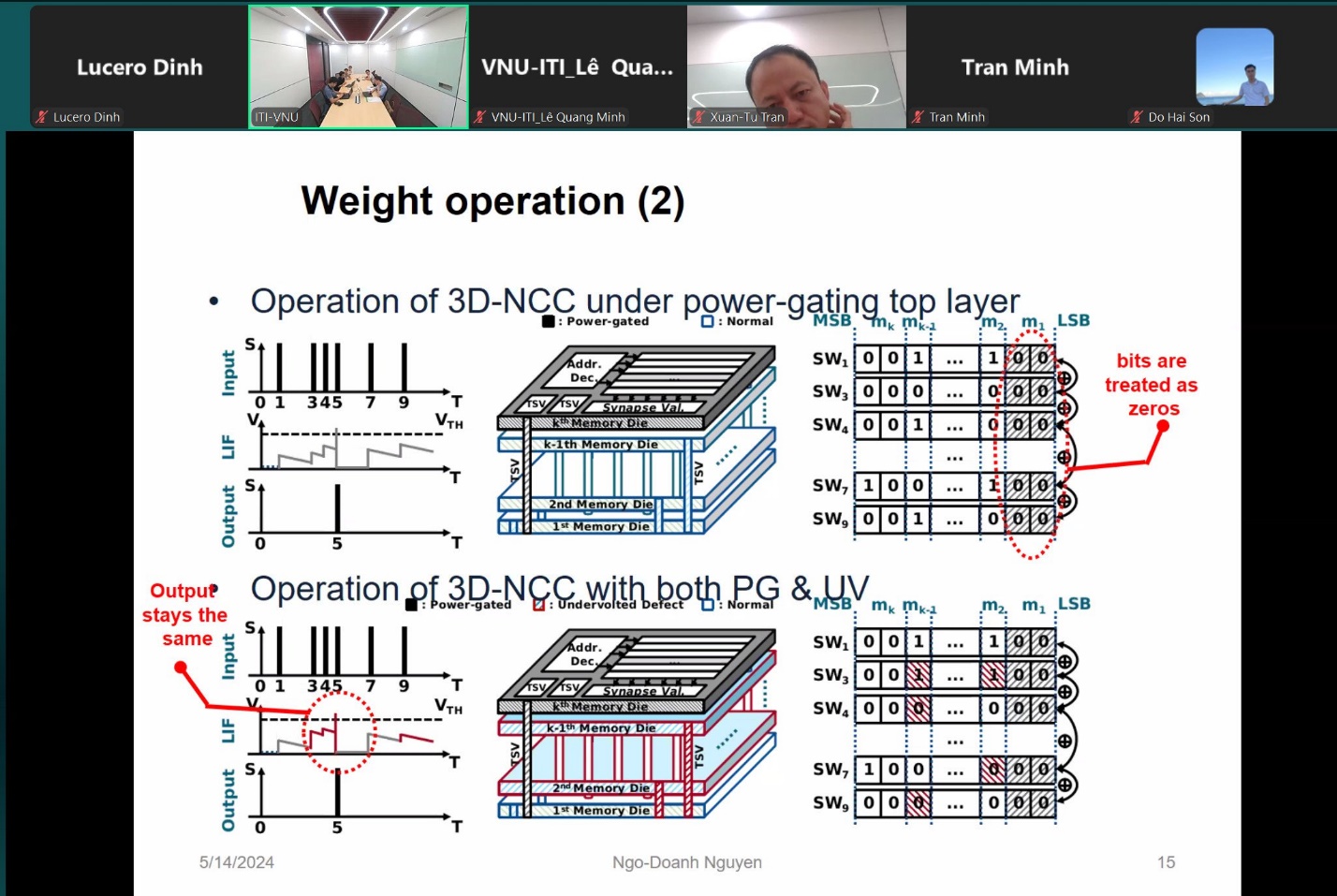

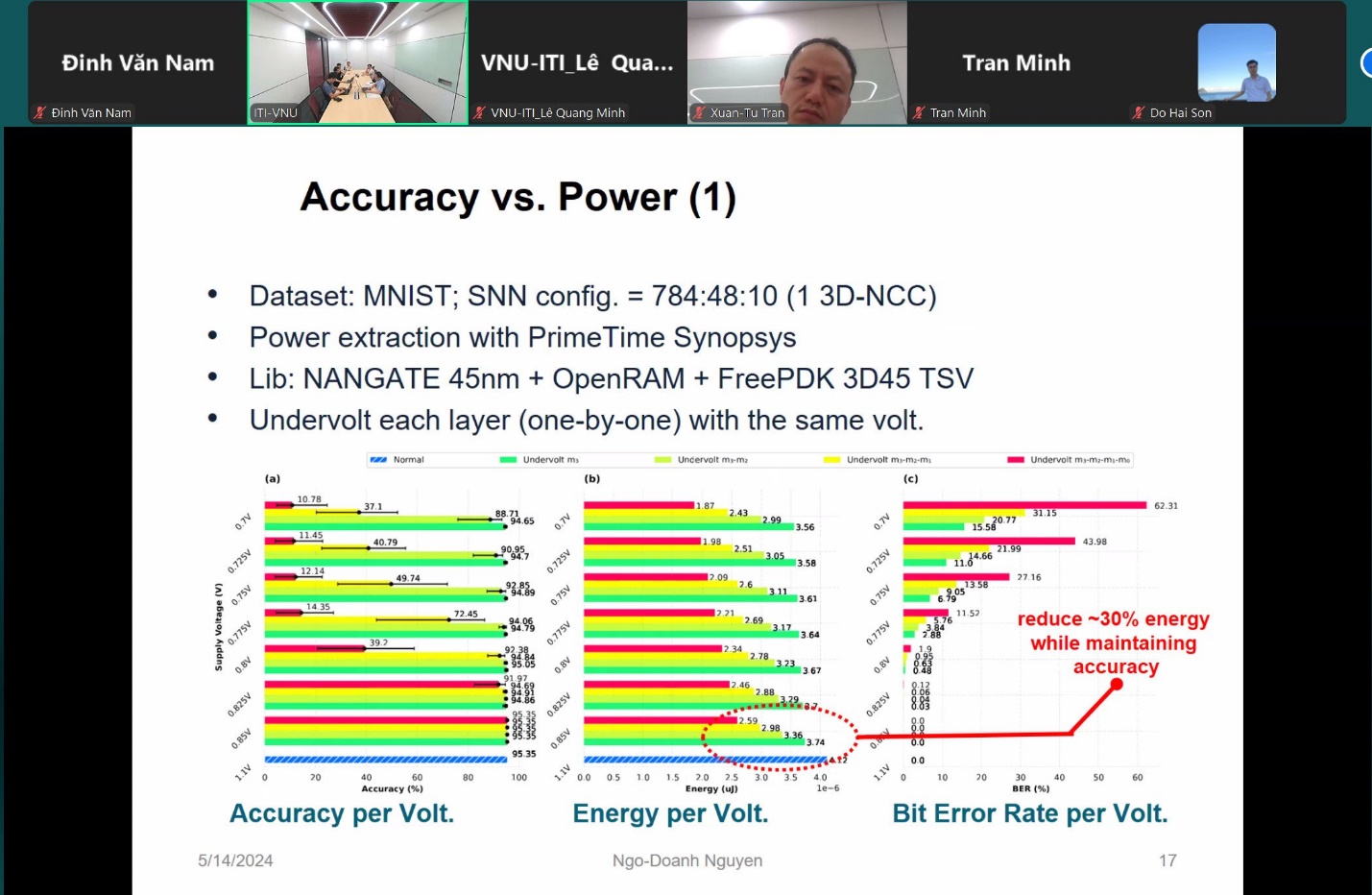

Bài thứ hai của buổi seminar của diễn giả Nguyễn Ngô Doanh là Thạc sĩ, nghiên cứu viên hiện đang làm việc tại Viện Công nghệ Thông tin. Bài báo cáo với chủ đề “Mạng nơ-ron mạch tích chập 3D công suất thấp”. Sự kết hợp giữa mạng nơ-ron spiking (SNN) và mạch tích hợp 3D giúp tiết kiệm năng lượng và tăng hiệu suất. Tuy nhiên, chỉ chuyển SNN vào cấu trúc 3D không thể khai thác hết tiềm năng của nó. Bài báo cáo này giới thiệu các tận dụng hiệu quả về mặt năng lượng của SNN bằng cách xếp chồng nhiều lớp bộ nhớ và chia trọng số synapse thành các tập hợp con trong các lớp cách ly khác nhau. Các kỹ thuật tiết kiệm năng lượng như ngắt nguồn và điều chỉnh điện áp được áp dụng cho từng lớp riêng biệt tùy theo tầm quan trọng của của các bit trọng số synapse. Mặc dù việc điều chỉnh điện áp có thể dẫn đến việc giảm độ chính xác của mạng nơ-ron nhưng hiệu suất của toàn bộ SNN chỉ giảm nhẹ so với hoạt động bình thường.