Trong bối cảnh các công nghệ bảo mật ngày càng phát triển, những thuật toán mã hóa như AES được xem là có độ an toàn cao, gần như không tồn tại lỗ hổng về mặt lý thuyết. Tuy nhiên, thực tế triển khai trên phần mềm và phần cứng lại cho thấy một nguy cơ khác — đó là sự rò rỉ thông tin thông qua các kênh kề (side-channel information) như công suất tiêu thụ, thời gian thực thi hay phát xạ điện từ trường. Những tín hiệu tưởng chừng vô hại này lại có thể bị lợi dụng để truy ra khóa bí mật trong thời gian rất ngắn, làm suy yếu đáng kể tính bảo mật của hệ thống.

Các nghiên cứu đã chỉ ra rằng, chỉ với khoảng một trăm lần thu thập lưu vết công suất tiêu thụ và dữ liệu đầu ra, kẻ tấn công có thể bẻ khóa AES trên các vi điều khiển thông thường trong vài phút, trong khi các phương pháp tấn công truyền thống như vét cạn (brute force) có thể mất hàng năm trời. Điều này đặt ra yêu cầu cấp thiết phải đánh giá mức độ an toàn của các thiết kế phần cứng không chỉ ở khía cạnh thuật toán, mà còn trong toàn bộ quá trình thực thi và vận hành.

Tuy nhiên, quy trình kiểm thử bảo mật phần cứng hiện nay đòi hỏi nhiều công đoạn phức tạp và tốn kém. Các nhà thiết kế phải hoàn thiện mô tả thiết kế ở mức chuyển dịch thanh ghi (RTL), tiến hành tổng hợp, mô phỏng, sau đó chế tạo chip thử nghiệm trên công nghệ ASIC hoặc nạp lên FPGA để thu thập lưu vết công suất thực tế trước khi có thể đánh giá mức độ an toàn. Nếu sau khi sản xuất mới phát hiện ra lỗ hổng bảo mật, toàn bộ quá trình chế tạo trở nên lãng phí cả về thời gian lẫn chi phí, đặc biệt với những ứng dụng yêu cầu độ bảo mật cao như thẻ ngân hàng, căn cước công dân điện tử hay thiết bị quốc phòng.

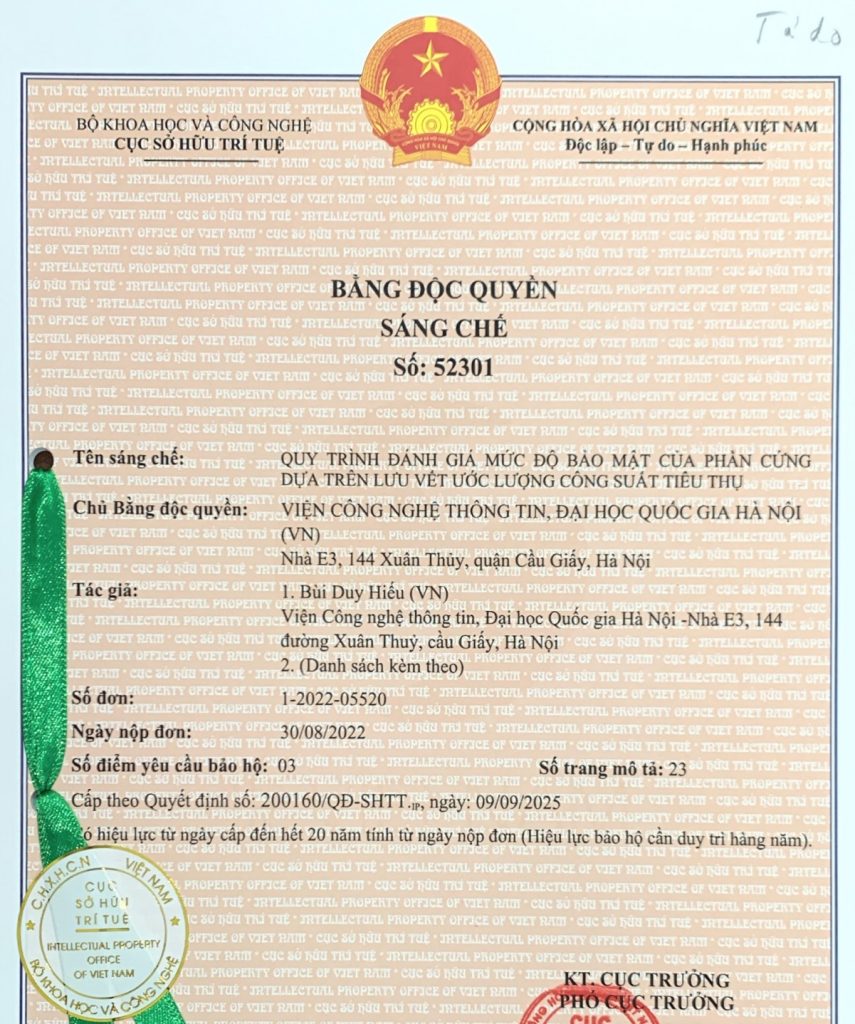

Nhằm giải quyết vấn đề này, Nhóm nghiên cứu Hệ thống tích hợp thông minh (SISLAB), Viện Công nghệ Thông tin – Đại học Quốc gia Hà Nội đã đề xuất một quy trình hoàn toàn mới: đánh giá mức độ bảo mật của phần cứng dựa trên lưu vết ước lượng công suất tiêu thụ ngay từ giai đoạn thiết kế, trước khi gửi đi chế tạo. Thay vì phải thu thập dữ liệu công suất thật từ chip vật lý, quy trình này cho phép ước lượng và mô phỏng lưu vết công suất thông qua các thông số của thiết kế — như mô hình thời gian, mạng điện, hay tham số ký sinh — để tái hiện gần đúng mức tiêu thụ năng lượng của mạch trong quá trình hoạt động. Các lưu vết này sau đó được phân tích bằng các kỹ thuật tấn công kênh kề phổ biến như phân tích tương quan công suất (CPA) hoặc phân tích vi sai công suất (DPA) nhằm phát hiện những điểm rò rỉ thông tin tiềm ẩn.

Nhờ cách tiếp cận này, các nhà thiết kế có thể phát hiện sớm các lỗ hổng bảo mật, xác định những khối mạch có nguy cơ rò rỉ cao và đưa ra giải pháp khắc phục ngay trong giai đoạn thiết kế — chẳng hạn như bổ sung kỹ thuật che giấu (masking), cân bằng tải hoặc ngẫu nhiên hóa thời gian xử lý. Việc phát hiện và xử lý sớm không chỉ giúp đảm bảo mức độ an toàn của thiết bị mà còn tiết kiệm đáng kể chi phí, thời gian, cũng như giảm thiểu rủi ro trong giai đoạn sản xuất hàng loạt.

Sáng chế về quy trình đánh giá bảo mật phần cứng dựa trên lưu vết ước lượng công suất tiêu thụ không chỉ mang ý nghĩa kỹ thuật mà còn thể hiện một tư duy đổi mới trong lĩnh vực thiết kế vi mạch. Đây là một bước tiến quan trọng trong việc chuyển hoạt động kiểm chứng bảo mật từ giai đoạn sau chế tạo lên giai đoạn trước chế tạo, góp phần nâng cao năng lực phát triển các sản phẩm phần cứng an toàn, đáng tin cậy, phục vụ cho các ứng dụng quan trọng trong lĩnh vực tài chính, nhận dạng và an ninh quốc gia.